微操作与控制器

微操作

执行程序时,计算机操作是由一系列指令周期组成的

- 每个周期执行一条机器指令

每个指令周期可以看作是由几个更小的子周期组成

- 取指、间指、执行、中断

微操作:每个子周期由一系列涉及CPU寄存器操作的更小步骤组成

微操作分组原则:

事件流动顺序必须是恰当的

必须避免冲突

- $MBR \leftarrow 内存$ 和 $IR \leftarrow MBR$ 不应出现在同一时间单位

所用的时间单位尽可能少

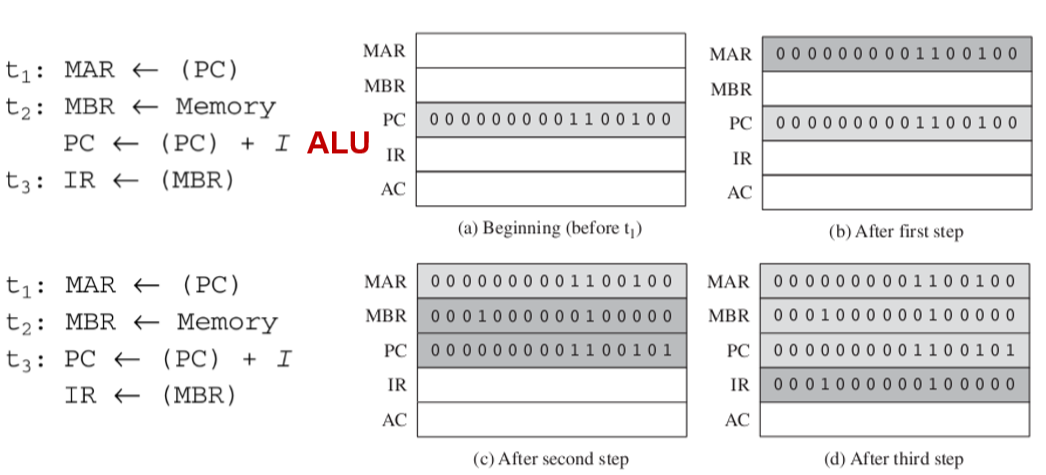

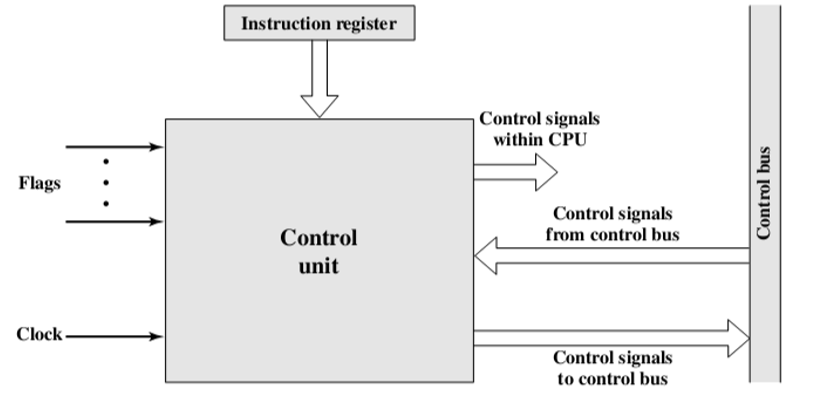

取指周期

出现在每个指令周期的开始,将指令从存储器中取出

时间要尽可能少,提高效率

涉及同一个设备或具有逻辑先后顺序的不能同时进行

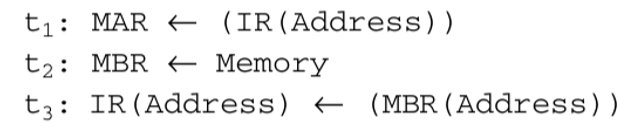

间址周期

若指令采用间接寻址,则在指令执行前有一个间址周期

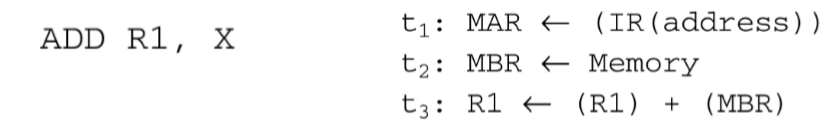

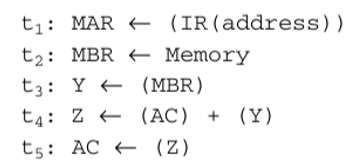

执行周期

对于不同的操作码,会出现不同的微操作序列

- 加法指令

- 转移并保存地址指令

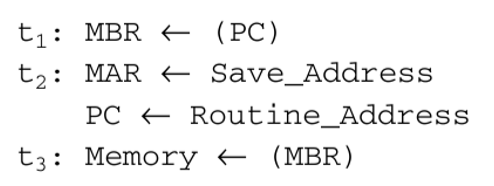

中断周期

在完成执行周期时,要确定是否有允许的中断产生

如果有,则出现一个中断周期

$MAR \leftarrow Save_Address$ 和 $Memory \leftarrow (MBR)$ 划掉

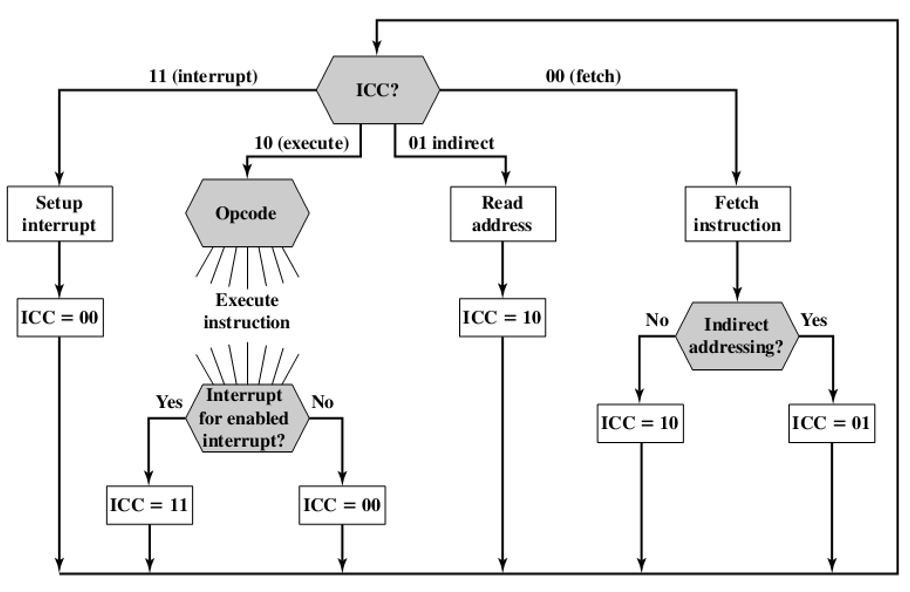

指令周期代码

取指、间址、中断周期各有一个微操作序列,执行周期对于每个操作码有一个微操作序列

指令周期代码:假设一个2位的ICC寄存器,明确CPU处于指令周期哪个阶段

00:取指

01:间址

10:执行

11:中断

控制器

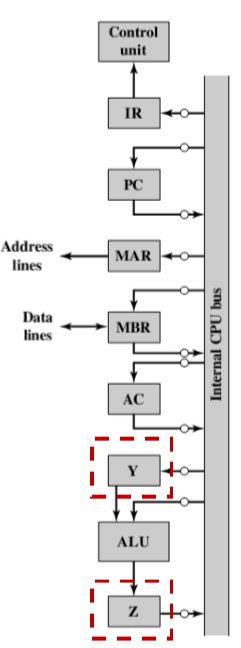

CPU内部总线

ALU和寄存器都连在CPU内部总线上

为了数据在该内部总线和各寄存器之间传递,内部总线和寄存器之间有门和控制信号

控制线控制着数据和系统总线(外部)的交换以及ALU的操作

控制CPU的功能需求

CPU的基本元素

- ALU、寄存器组、内部数据通路、控制器、外部数据通路

CPU需要完成的微操作

在寄存器之间传送数据

将数据由寄存器传送到外部接口(如系统总线)

将数据由外部接口传送到寄存器

将寄存器作为输入和输出,完成算术和逻辑运算

控制器的两个基本任务

定序:根据正被执行的程序,控制器使CPU以正确的顺序通过一系列微操作

执行:控制器使每个微操作得以完成

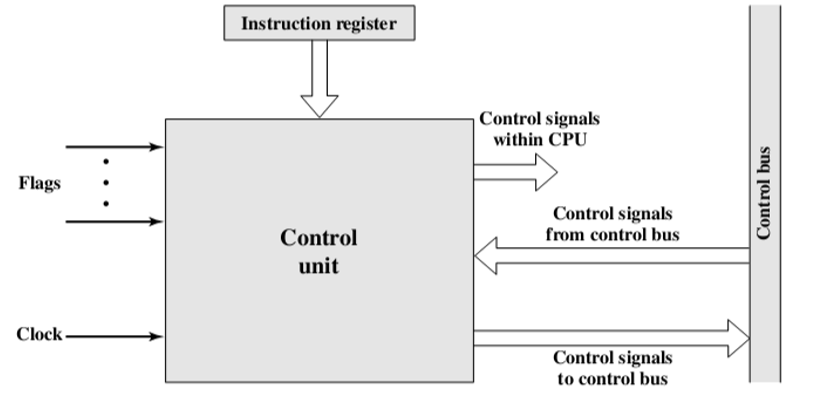

控制器的输入和输出

输入

指令寄存器:当前指令的寻址方式和操作码

标志:确定CPU状态和前一个ALU操作的结果

时钟:控制器要在每个时钟脉冲完成一个或一组同时的微操作

来自控制总线的控制信号:向控制器提供控制信号

输出

CPU内的控制信号:

用于寄存器之间传送数据

用于启动特定的ALU功能

到控制总线的控制信号:

到存储器的控制信号

到I/O模块的控制信号

所有控制信号最终作为二进制输入量直接输入到各个逻辑门上

控制信号

所有控制信号最终都作为二进制输入直接应用于各个逻辑门

三种控制信号:

激活ALU的功能

激活数据通路

通过系统总线或其他外部接口传递来的信号

举例:

传送PC的内容到MAR

- 打开$C_2$:PC传到MAR

由存储器读一条指令装入MBR,并且递增PC

打开$C_0$:MAR的内容送到地址总线上

存储器读控制信号$C_R$送到控制总线上

打开$C_5$:数据总线上的内容存入MBR

控制信号对PC内容加以,并把结果存回PC

传送MBR的内容到IR

- 打开$C_4$:MBR的内容送到IR

小圆点表示的是门,$C_R$是读信号

一个固定长度二进制串用来控制相应的门的开关

控制器的最小特性

它只需要知道将被执行的指令和算术、逻辑运算结果的性质(比如正负、溢出等)

- 不需要知道正被处理的数据或得到的实际结果是什么

它只是以少量的送到CPU内的和送到系统总线上的控制信号来实现控制

控制器实现

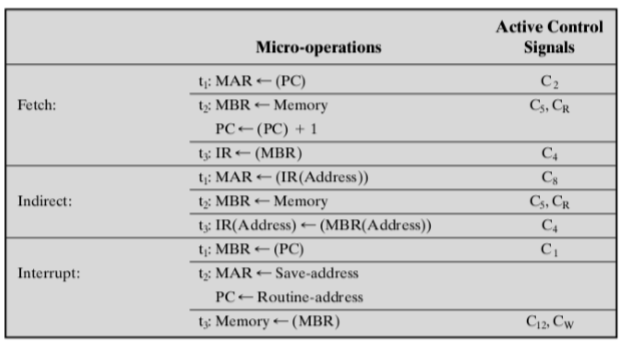

硬布线实现

- 控制器是一个组合电路,把输入逻辑信号转换为一组输出逻辑信号,即控制信号

微程序实现

- 控制逻辑是微程序指定的,控制器是一个相对简单的逻辑电路,通过执行每条微指令来产生控制信号

硬布线实现

标志和控制总线信号:每位都有特定意义

指令寄存器:通过译码使得每一个操作码有一个唯一的逻辑输入

- $n$个输入 $\rightarrow$ $2^n$个输出

时钟:在一个时钟周期内,控制器在不同时间单位发送不同的控制信号

使用一个定时器作为控制器的输入,并且控制器在指令周期结束时必须通知定时器使其重新开始计数

时钟脉冲的周期必须足够长,以允许信号沿数据路径和通过处理器电路传播

控制器逻辑

为每个输出的控制信号设计一个关于控制器输入的布尔表达式

定义两个控制信号 $P$ 和 $Q$

$PQ = 00$:取指周期

$PQ = 01$:间址周期

$PQ = 10$:执行周期

$PQ = 11$:中断周期

举例:

$C_5$:使外部数据总线上的数据读入MBR

$C_5$ 在取指和间址周期的第二个时间单位有效:

- $C_5 = \bar{P} \cdot \bar{Q} \cdot T_2 + \bar{P} \cdot Q \cdot T_2$

$C_5$ 在执行周期也有效:

- $C_5 = \bar{P} \cdot \bar{Q} \cdot T_2 + \bar{P} \cdot Q \cdot T_2 + P \cdot \bar{Q} \cdot (LDA + ADD + AND) \cdot T_2$

微程序实现

微程序基于硬件和软件之间

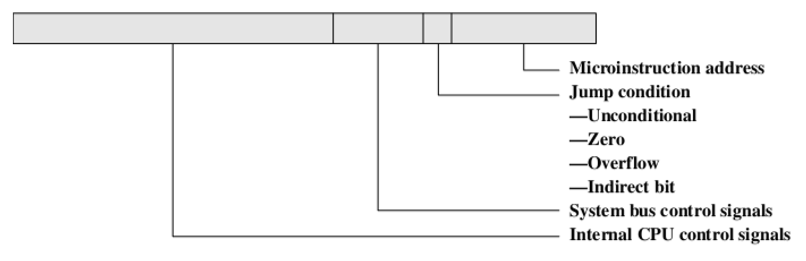

微指令:每行描述一个时间内出现的一组微操作

基本思路:

对于每个微操作,控制器的任务是产生一组控制信号

构造一个控制字,每位代表一根控制线

- 这样每个微操作能用控制字中不同的0和1的样式来表示

将这些控制字串在一起,可以表示控制器需要完成的微操作序列

由于每个微操作的顺序不是固定的,控制字被放入存储器中,每个字都有一个唯一的地址

添加少数几位用于指示条件的真假

假则顺序执行下一条指令

真则地址字段指向的微指令是下一条执行的微指令

地址字段:指示条件为真时,将要执行的下一控制字的位置

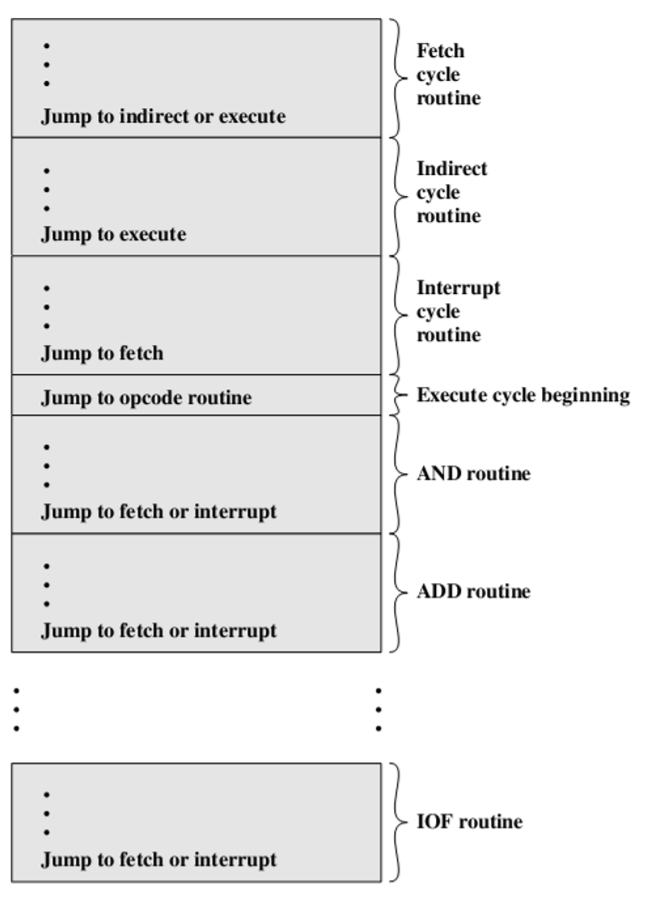

微程序执行:

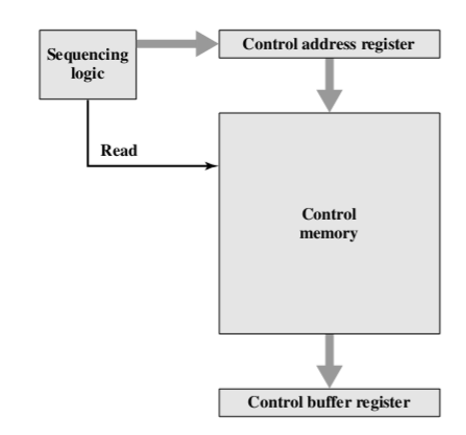

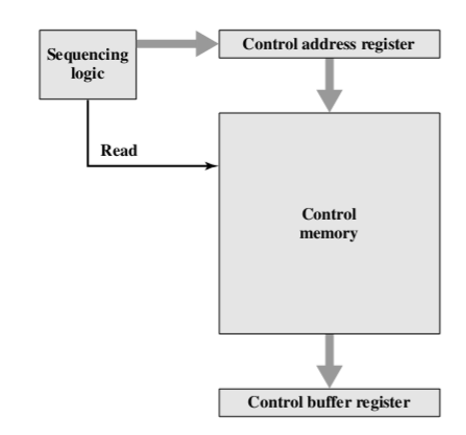

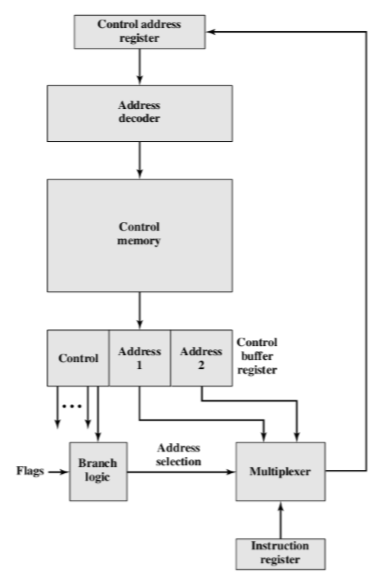

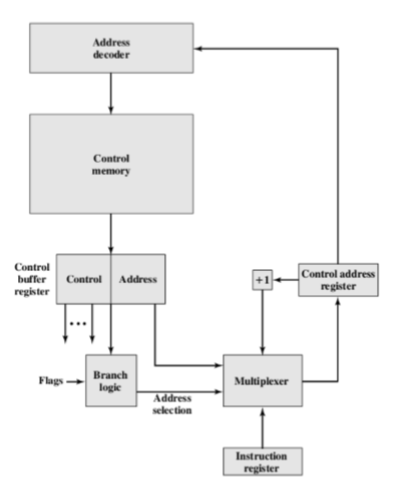

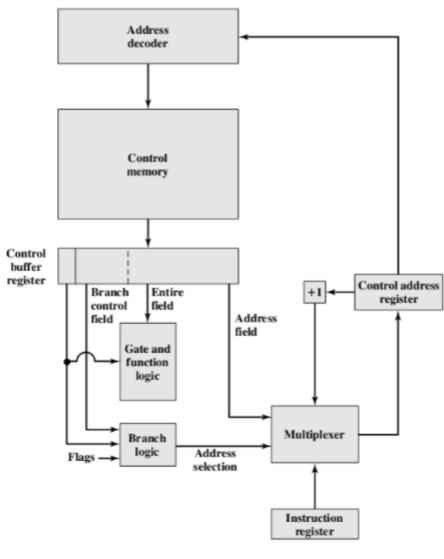

微程序控制器构成

定序逻辑:向控制地址寄存器装入地址,并发出读命令

控制地址寄存器:含有下面即将被读取的微指令地址

控制存储器:存有一组微指令

控制缓冲寄存器:存放被读出的微指令

微程序控制器任务

微指令定序

根据当前的微指令、条件标志和指令寄存器的内容,产生下一微指令的控制存储器地址

双地址字段:在每条微指令中提供两个地址字段,选择并发送其中某一个地址或操作码到控制地址寄存器

单地址字段:下一个地址得选择可以是地址字段或下一个顺序地址

可变格式:提供两种完全不同的指令格式,一位字段用于指定哪种格式被使用

设计考虑:

微指令的大小

地址生成时间

微指令执行

产生控制信号:发往CPU内部,送往外部控制总线或其他外部接口

微程序控制器工作流程

为执行一条指令,定序逻辑发出一个读命令给控制存储器

当一条微指令由控制存储器读出后,被传送到控制缓冲寄存器

- 从控制地址寄存器读

控制缓冲寄存器的内容生成控制信号,并为定序逻辑提供下一条地址信息

控制缓冲寄存器的左半部分与控制器发出的控制线相连

由控制存储器读一条微指令等同于执行这条微指令

定序逻辑根据这个地址信息和ALU标志,将新的地址装入到控制地址寄存器

生成新地址的三个选择:

取顺序下一条微指令:加1到控制地址寄存器

基于跳转微指令转移到一个新的例程:将控制缓冲寄存器的地址字段装入控制地址寄存器

转移到一个机器指令例程:根据IR总的操作码向控制地址寄存器装入机器指令例程的第一条微指令